Sin categoría

Digital Clock (part 3) – Counter and multiplexer

When I started this project back in the spring of 2016 I did not think for a moment that it would take so long to finish it. But the fact is that between whistles and flutes I left it super abandoned. While I was waiting to finish the TFG I was unable to get any project and then this part of the circuit is more complex and until I ordered the PCB to China, it has not worked.

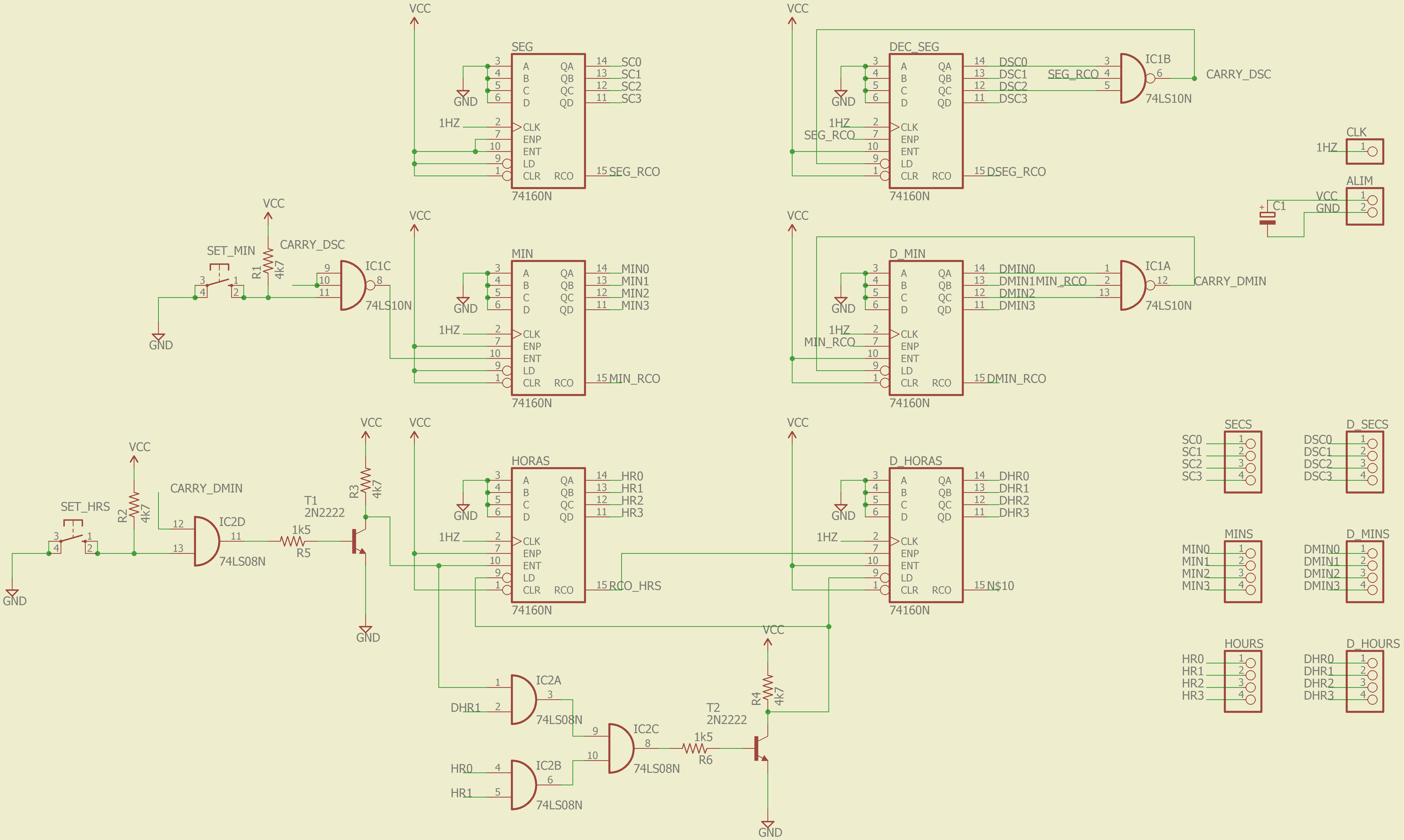

COUNTER

The part of the counter corresponds to the clock's nucleus, since the pulses are counted in cascade to count minutes, tens of minutes, etc. I have based the design on an example of Proteus 7 changing things for my specific project. The most difficult thing at the time was finding the abovementioned counters SN74LS160N. In the case of integrated circuits of the 70's plus the AIDS that give the electronics stores in Madrid, well let's say I had to go through several stores and I did not get anything cheap 74XX chips. First I tried to make one sided PCB, but I was not very skillfull with the acid and many airwires came out, let's say everything was aimed to fail. Obviously, the PCB did not work. Finally I placed and order at JLC PCB.

The schematic is the following:

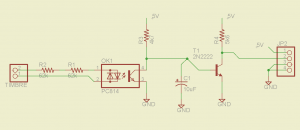

The reason for using AND gates and inverters with a BJT is that when I went to buy the IC's there was only a 74LS10 (3x 3-input NAND) and there were no 4-input ANDs, so I bought a 74LS08 (4x 2-input AND) and I managed with two transistors. Without going into much detail, the count enable of each counter is fed by the overflow of the previous one. Despite being counters with a 4-bit output, being decimals, the overflow occurs automatically in the transition from 9 to 10.