En la asignatura de Sistemas electrónicos digitales, como trabajo nos encargaron a mí y a mis compañeros realizar un reloj en VHDL. VHDL es un lenguaje de programación de descripción Hardware que dista un poco de la concepción de programación que se tiene de programar lenguajes de alto nivel como C/C++, pero que para cosas como éstas, pues se acaba haciendo intuitivo. Incluso una de las modalidades de programación (Behavioral) hace que se parezcan bastante.

Dispusimos de:

- FPGA Spartan3 de Xilinx.

- ISE Design Suite 14.7.

- Sublime Text 2.

- Bitbucket.

Con la herramienta ISE compilamos, testeamos y preparamos el código para una vez finalizado, subirlo a la placa para ver que funcionaba. Lo bueno que tiene este programa es que se pueden genarar ficheros de simulación para ver como se comporta lo que hemos programado y la verdad es que ayuda bastante. Lo que mas problemas nos dió fue construir la entidad TOP para cargarlo a placa,pues no lo teniamos muy claro. Una vez probados todos los módulos con los testbench, subimos el código a placa.

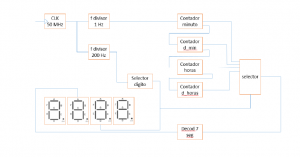

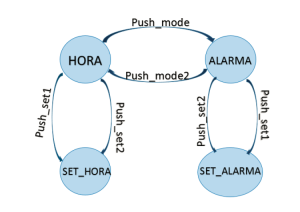

El reloj tiene las siguientes funcionalidades:

- 24h

- Alarma

- Posiblidad de ajustar hora y alarma

Usamos los leds que tiene la spartan para indicar el modo de funcionamiento, y la alarma, asi como los interruptores para cambiar de modo. Lo de los interruptores funcionó algo mal por los rebotes en los cambios de estado, pero eso no nos dio tiempo a mejorarlo.

Usamos una maquina de estados para las funcionalidades.

El proyecto me gustó tanto que he decidido hacerme un reloj digital basándome en éste, pero con lógica TTL y CMOS con los integrados de la serie 7400 y 4000.

Aquí tenéis un breve video donde se ve funcionando el reloj, desgraciadamente no tengo mejores videos, una pena 🙁

2 comentarios

Josue-Jair Vicencio-Gonzalez · junio 27, 2017 a las 12:49 pm

Puedes pasarme el archivo en ise, por favor gracias

picatostasadmin · junio 27, 2017 a las 10:09 pm

No conservo los archivos, lo siento !