In the subject of digital electronic systems, as work, they asked me and my colleagues to make a watch in VHDL. VHDL is a hardware description programming language that is far from the conception of programming that is to program high-level languages such as C / C ++, but for things like these, it ends up being intuitive. Even one of the programming modalities (Behavioral) makes them look alike.

We had:

- FPGA Spartan3 from Xilinx.

- ISE Design Suite 14.7.

- Sublime Text 2.

- Bitbucket.

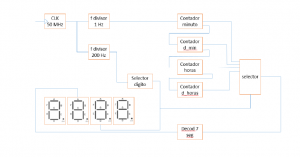

With the ISE tool we compile, test and prepare the code for once completed, upload it to the board to see what worked. The good thing about this program is that you can generate simulation files to see how what we have programmed behaves and the truth is that it helps a lot. What gave us more problems was to build the entity TOP to load it to plate, because we did not have it very clear. Once all the modules with the testbench have been tested, we upload the code to the board.

The watch has the following features:

- 24h

- Alarm

- Possibility of setting time and alarm

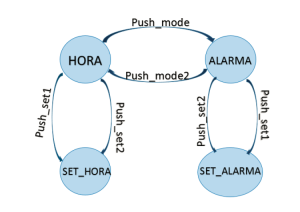

We use the LEDs that the spartan has to indicate the mode of operation, and the alarm, as well as the switches to change the mode. The switches worked badly because of the rebounds in the changes of state, but that did not give us time to improve it.

We use a state machine for functionalities.

The project I liked so much that I decided to make a digital clock based on it, but with TTL and CMOS logic with the integrated series 7400 and 4000.

Here you have a short video where you see the clock running, unfortunately I do not have better videos, a pity 🙁

https://youtu.be/hvT_GbVZBHc

0 Comments